Tutorial creare proiect Vivado

Pentru a crea un proiect în Vivado cu ajutorul căruia puteți sintetiza cod pe FPGA urmați pașii de mai jos:

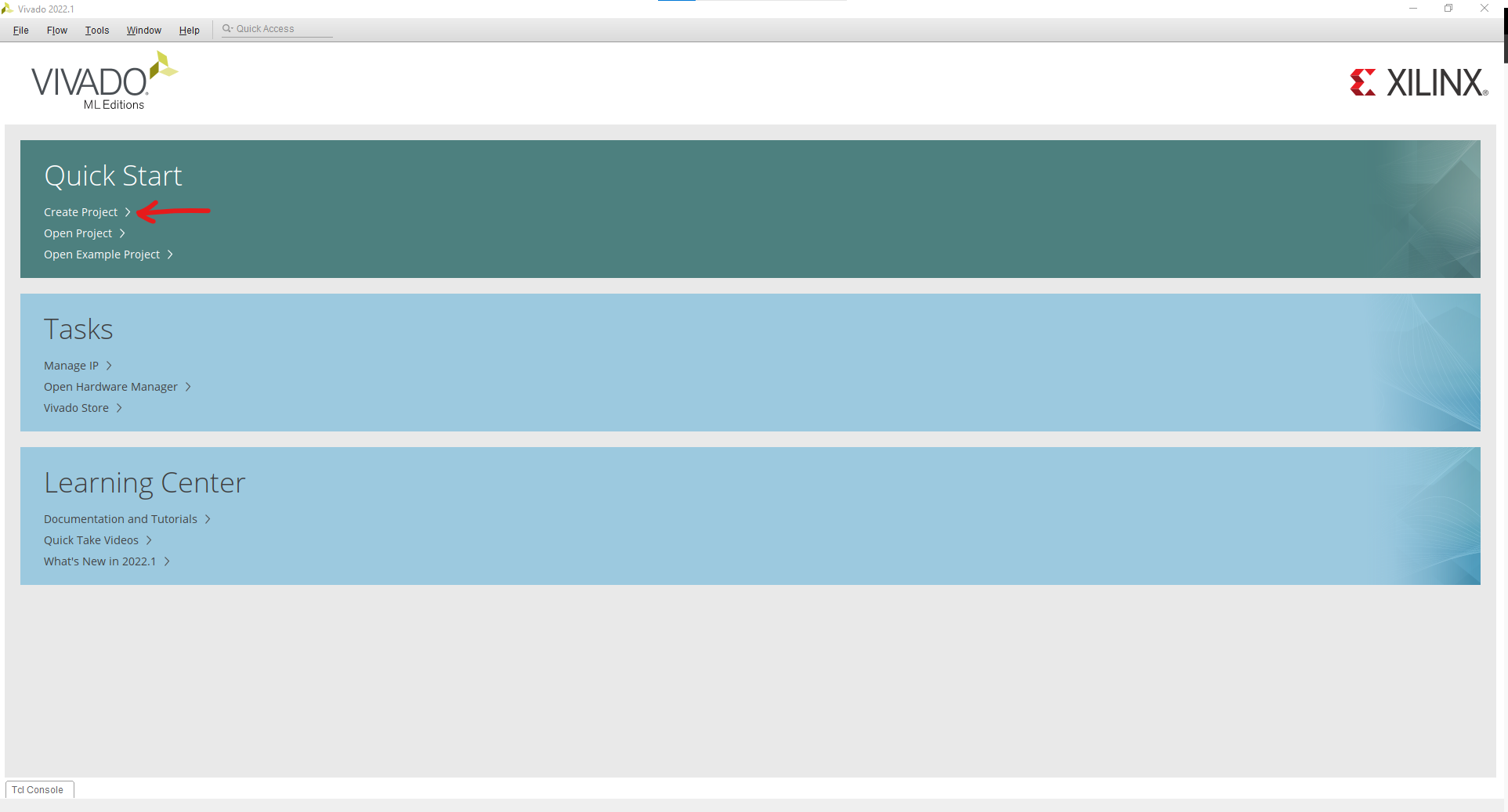

- Deschideți programul Vivado și selectați Create Project

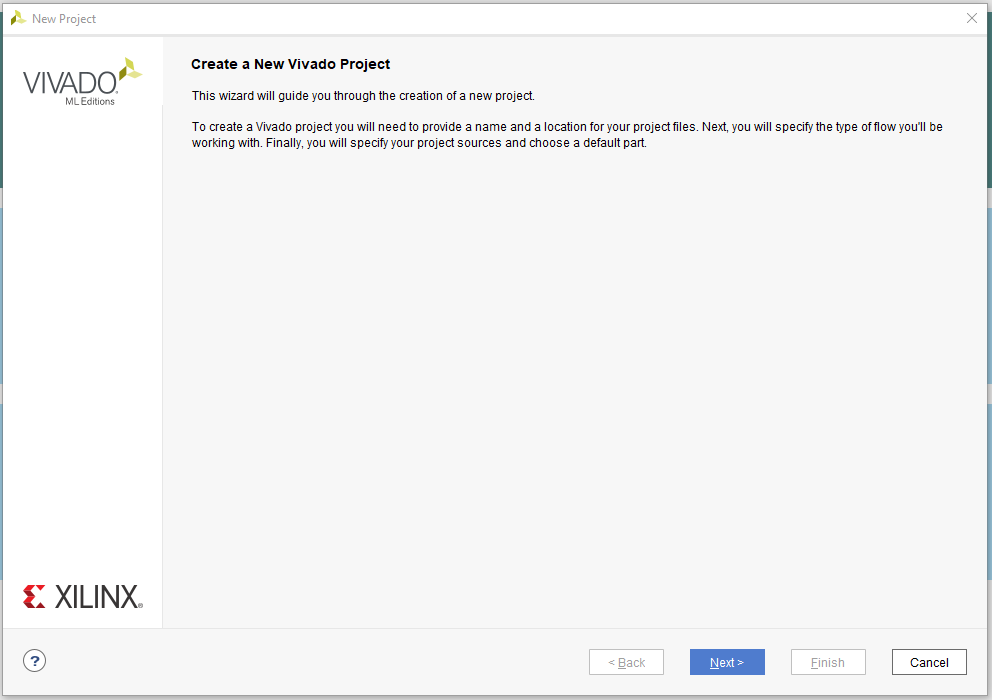

- Apasați Next

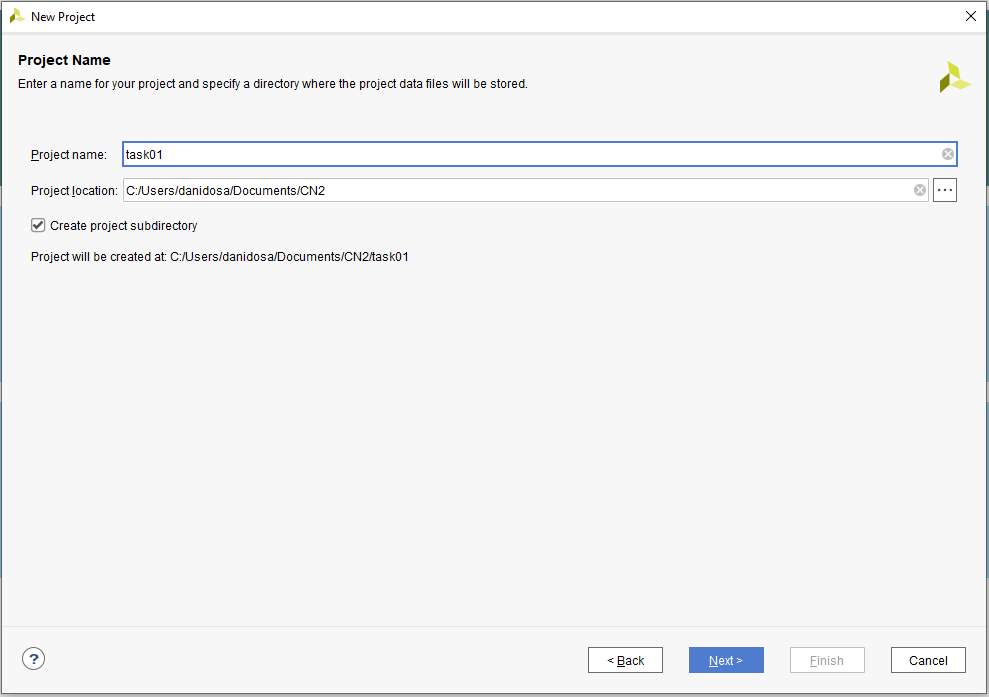

- Scrieți numele proiectului și selectați locația acestuia.

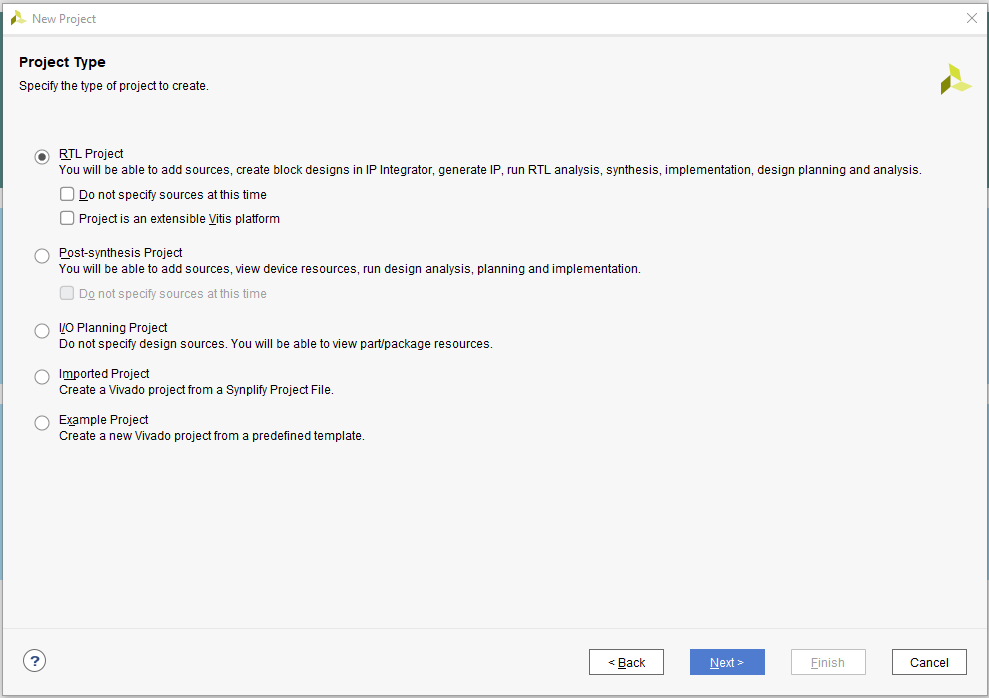

- Selectați RTL Project, deselectați "Do not specify sources at this time" și apăsați Next

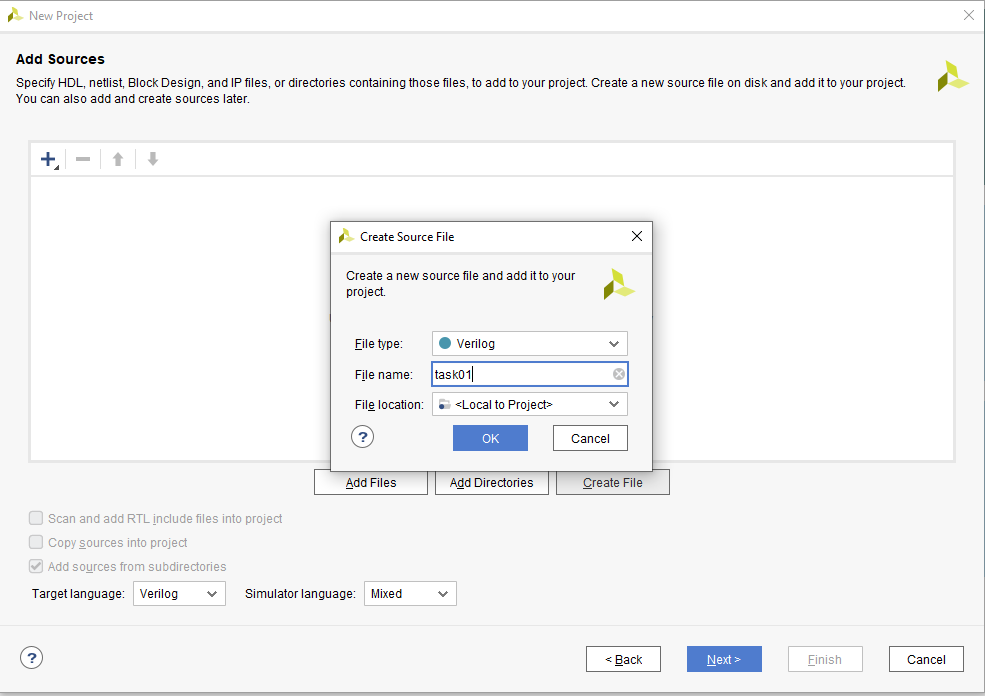

- Apăsați "Create File" și alegeți un nume pentru fisierul sursă. Asigurați-vă că Target Language este "Verilog" și apăsați Next.

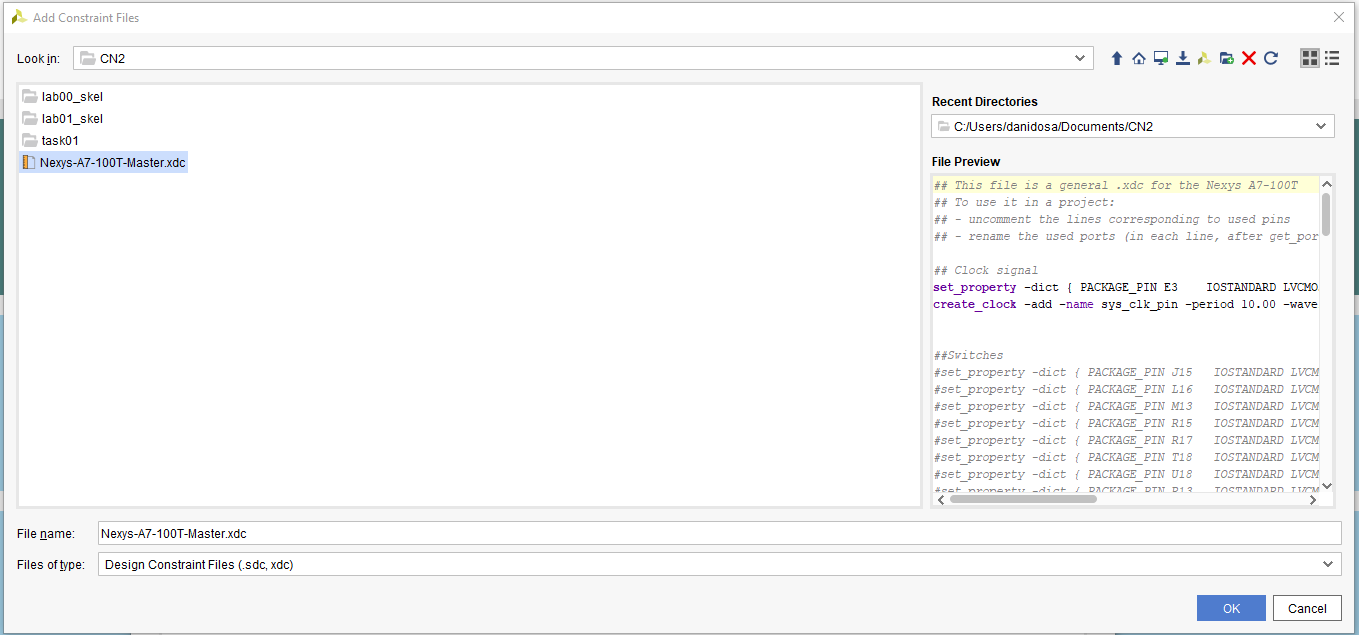

- [Opțional - doar pentru programarea unui FPGA - puteți apăsa pe Next pentru a sări peste acest pas] Adăugați un constraint file (Ce reprezintă un astfel de fișier?) pentru placa FPGA pe care o folosiți (De exemplu Nexys-A7-100T-Master.xdc - descarcați acest fisier!) (Add Files -> Cautati si selectati fisierul "Nexys-A7-100T-Master.xdc" -> Next)

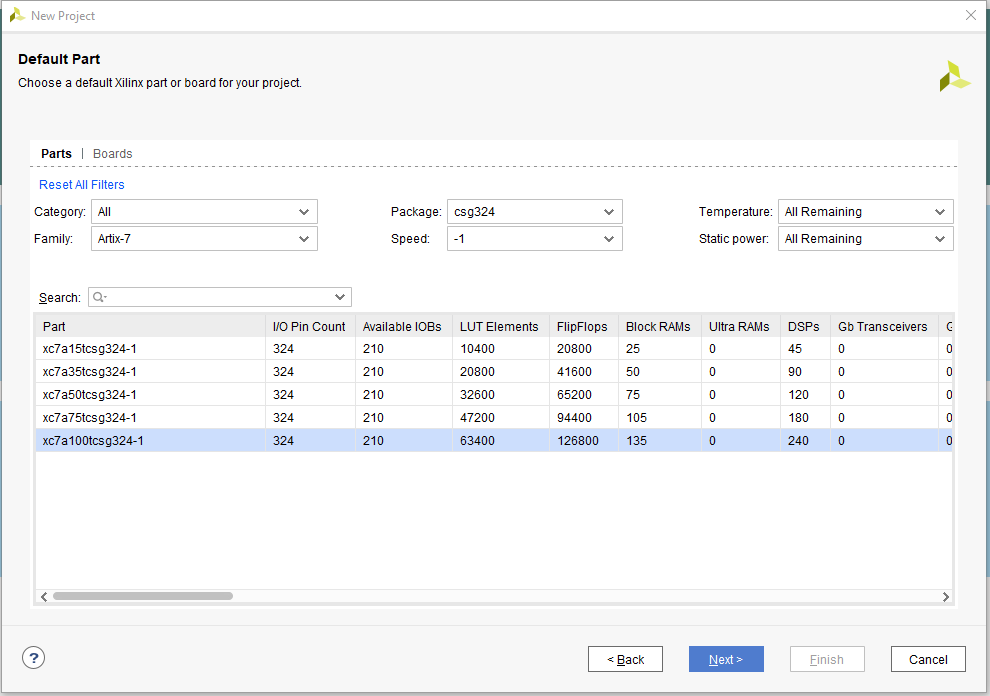

- Selectați caracteristicile plăcii FPGA: Category, Familiy, Package, Speed (Le veți găsi pe cutia plăcuței sau în reference manual) - Exemplu pentru

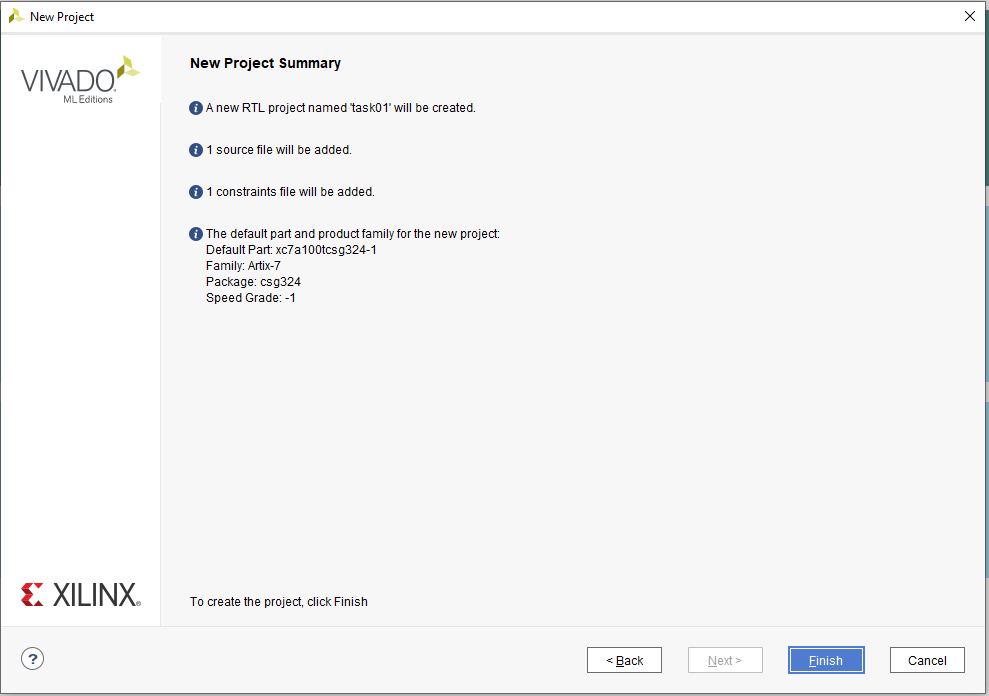

- Revizuiți informațiile proiectului

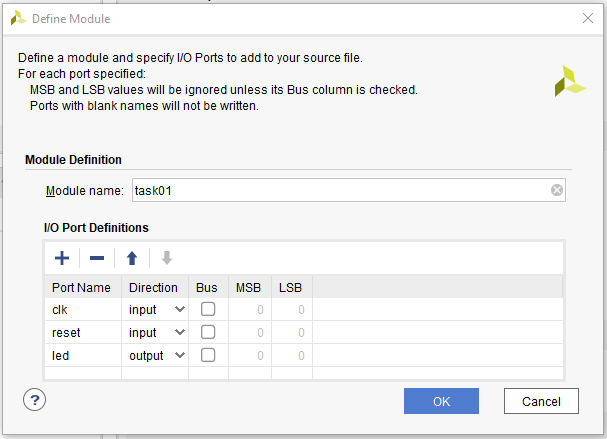

- La acest pas puteți defini numele modulului și porturile acestuia:

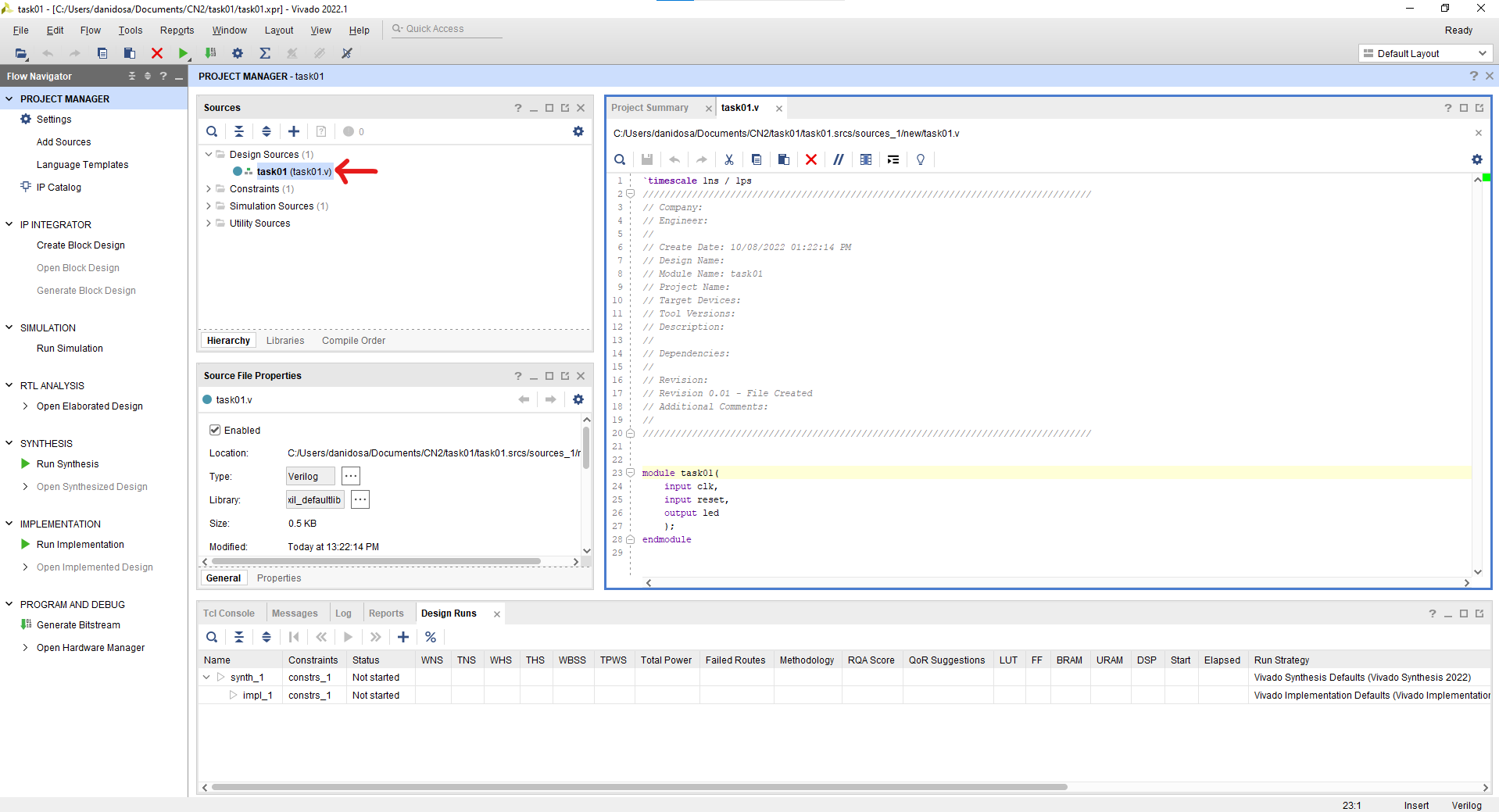

- În final, în Vivado veți putea vizualiza proiectul astfel

.

.

În stânga ecranului putem vedea pașii de simulare, sintetizare, implementare și generare a bitstream-ului ce va fi folosit pentru configurarea interna a FPGA-ului.

Dacă aveți sugestii de îmbunătățire a acestei pagini vă rog să trimiteți sugestiile pe mail la dosarudaniel@gmail.com.